Advertisements

Advertisements

प्रश्न

An X-OR gate has following truth table:

| A | B | Y |

| 0 | 0 | 0 |

| 0 | 1 | 1 |

| 1 | 0 | 1 |

| 1 | 1 | 0 |

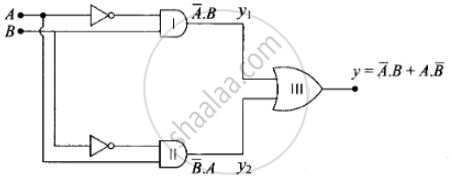

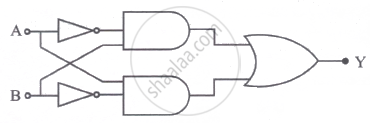

It is represented by following logic relation `Y = barA.B + A.barB`. Build this gate using AND, OR and NOT gates.

Advertisements

उत्तर

X-OR gate can be realized by the combination of two NOT gates, two AND gates and one OR gate. According to the problem, the logic relation for the given truth table is

When `Y = barA * B + A * barB = Y_1 + Y_2`

`Y_1 = A * B` and `Y_2 = A * barB`

Y1 can be obtained as output of AND gate 1 for which one input is of A through NOT gate and another input is of B. Y2 can be obtained as the output of AND pate II for which one input is of A and the other input is of B through NOT gate.

Now Y can be obtained as output from OR gate, where Y1 and Y2 are inputs of OR gate.

Thus, the logic circuit of this relation is given below.

APPEARS IN

संबंधित प्रश्न

The following figure shows the input waveforms (A, B) and the output waveform (Y) of a gate. Identify the gate, write its truth table and draw its logic symbol.

The logic gate which produces LOW output when one of the input is HIGH and produces

HIGH output only when all of its inputs are LOW is called _______.

(A) AND gate

(B) OR gate

(C) NOR gate

(D) NAND gate

You are given two circuits as shown in following figure, which consist of NAND gates. Identify the logic operation carried out by the two circuits.

(a)

(b)

Draw the schematic symbols for AND, OR, NOT and NAND gate

What will be the values of input A and B for the Boolean expression `overline ((A +B) .(A*B)) =1?`

The output of an OR gate is connected to both the inputs of a NAND gate Draw the logic circuit of this combinaion of getes and write its truth table.

Let \[X = A \overline{ BC} + B\overline{ CA} + C\overline{AB } .\] Evaluate X for A = 1, B = 0, C = 1.

Let \[X = A \overline{ BC} + B\overline{ CA} + C\overline{AB } .\] Evaluate X for A = B = C = 0.

Design a logical circuit using AND, OR and NOT gates to evaluate \[A \overline { BC } + B \overline{ CA }\] .

Show the variation of voltage with time, for a digital signal.

Draw the truth table of a NOR gate.

Draw a diagram to show how NAND gates can be combined to obtain an OR gate. (Truth table is not, required)

Useful Constants and Relations:

| 1. | Charge of a proton | (e) | =1.6 × 10-19C |

| 2. | Planck's constant | (h) | = 6·6 × 10-34 Js |

| 3. | Mass of an electron | (m) | = 9·1× 10-31 kg |

| 4. | Permittivity of vacuum | (∈0) | =8 · 85 × 10-12 Fm-1 |

| 5. | `(1/(4pi∈_0))` | =9 ×109 mF-1 | |

| 6. | Permeability of vacuum | (μ0) | = 4π × 10-7 Hm-1 |

| 7. | `((mu_0)/(4pi))` | =1 × 10-7 Hm-1 | |

| 8. | Speed of light in vacuum | (c) | = 3× 108 ms-1 |

| 9. | Unified atomic mass unit | (u) |

= 931 MeV |

| 10. | Electron volt | (leV) | = 1.6 × 10-19 J |

In potential barrier development in a junction diode opposes

The truth table for the following logic circuit is:

For the given circuit, the input digital signals are applied at terminals A, B, and C. What would be the output at terminal y?

For the given circuit, the input digital signals are applied at the terminals A, B and C. What would be the output at the terminal y?

How would you set up a circuit to obtain NOT gate using a transistor?